# **VLN5P Series (OTP)**

Single-Chip 4-bit MCU with 15~24 I/O, '1-Ch Speech + Dual-Tone' or '4-Ch Speech/Midi'

**Version 2.0**

Jun. 18, 2018

VOICELAND reserves the right to change this document without prior notice. Information provided by VOICELAND is believed to be accurate and reliable. However, VOICELAND makes no warranty for any errors which may appear in this document. Contact VOICELAND to obtain the latest version of device specifications before placing your orders. No responsibility is assumed by VOICELAND for any infringement of patent or other rights of third parties which may result from its use. In addition, VOICELAND products are not authorized for use as critical components in life support devices/systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of VOICELAND.

# 1. GENERAL DESCRIPTION

The VLN5P series IC is a powerful 4-bit micro-controller based sound processor. They are embedded EPROM architecture, and the OTP (One Time Programmable) ICs that are designed to support VLN5P and MaskROM products. There are 4 channels that are configured as speech, tone or midi, and all of them can be auto-played back simultaneously. By using the high fidelity ADPCM speech synthesis algorithm, it can produce outstanding quality voices. Wide range sampling rate up to 44.1kHz and different volume level are supported. It is also equipped two kinds of audio outputs with fine resolution, including a current D/A converter and a PWM direct-drive. The RISC MCU architecture is very easy to program and control, various applications can be easily implemented. There are 48 instructions, and most of them are executed in single cycle. Through +/-0.5% accurate internal oscillation, external Rosc is mostly unnecessary. Also an OSC pad is reserved for external oscillation, and this pad can be optioned as normal I/O when setting internal oscillation only. Furthermore, in addition to the HALT mode (sleep mode), it offers the SLOW mode to minimize power dissipation.

### 2. FEATURES

- Wide operating voltage range: 2.0V to 5.5V. (Same as MaskROM products)

- 4-bit RISC type micro-controller with 48 instructions.

- 1248Kx10-bit ROM maximum, program and voice data share the same ROM space. The voice duration,

ROM size and I/O counts are shown below.

| Product<br>(OTP) | Voice Duration (sec)<br>@6kHz | ROM Size (10-bit) | VO                      |

|------------------|-------------------------------|-------------------|-------------------------|

| VLN025-5S24J/B   | 25.0                          | 64k x 10          | 15 (PA, PB, PC, PD0~2)  |

| VLN085-5S24J/B   | 85.0                          | 208k x 10         | 15 (PA, PB, PC, PD0~2)  |

| VLN185-5S28J/B   | 185.0                         | 448k x 10         | 20 (PA, PB, PC, PD, PE) |

| VLN345-5S28J/B   | 345.0                         | 832k x 10         | 20 (PA, PB, PC, PD, PE) |

- 224x4-bit RAM maximum, divided into 4 pages.

- 1MHz instruction frequency.

- SLOW mode to operate at low power consumption. (Not suggest using in Timer/Clock application.)

- HALT mode to save power, less than 1uA@3V standby current.

- Precisely embedded oscillator with build-in resistor (+/- 0.5%). External resistor to adjust system frequency is optional.

- Low voltage reset (LVR=1.8V), watch-dog reset and I/O port reset are all supported to protect the system.

2

One interrupt entrance with an independent stack, multiple interrupt sources.

- Maximum 24 flexible I/Os maximum with optional function: input, output, large current output, IO, floating-type reset, pull-high reset, IR carrier output and large current IR carrier output. For the output port, users can select the normal Drive current output or large Sink current output to directly drive high brightness LED.

- Support Open-Drain (OD) bi-direction IO.

- Infrared output: optional IR carrier frequency and optional data high/low IR output supported.

- Maximum of 4 channels can play simultaneously; each channel can be arbitrarily assigned as speech, tone

or midi channel based on the product spec.

- New high fidelity ADPCM speech synthesis algorithm.

- 3 kinds of 256 points, ADSR and Full-Wave instrument waveform provide outstanding midi quality for MIDI.

- 256 steps envelope control for tone and MIDI.

- High quality 9-bit PWM to directly drive speaker, or 10-bit D/A converter audio output to amplify the volume by external audio amplifier for multi-channel MIDI especially.

- Support large PWM current output.

- 16 steps volume control for audio output.( J type don't support DAC mode, only using PWM mode)

- Quick-IO control supported.

- A unique fast writing mode is provided to speed up OTP writing time.

- A special ICP (In Circuit Programming) writing function is supported for user to fabricate PCBA in advance.

3

- Programmable code protection is provided. (When the Security-Bit is burnt down, data can't be read.)

- Various shipping type for different application requirement.

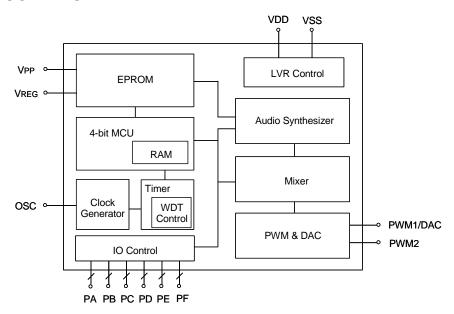

### 3. BLOCK DIAGRAM

# 4. PAD DESCRIPTION

| Pad Name         | ATTR. | Description                                                    |  |  |

|------------------|-------|----------------------------------------------------------------|--|--|

| V <sub>REG</sub> | Power | Regulator input. Connect a 0.1uF cap to GND or keep floating.  |  |  |

| VDD#             | Power | Positive power.                                                |  |  |

| GND#             | Power | Negative power.                                                |  |  |

| PA0              | I/O   | Bit 0 for Port A.                                              |  |  |

| PA1              | I/O   | Bit 1 for Port A,                                              |  |  |

| PA2~3            | I/O   | Bit 2~3 for Port A.                                            |  |  |

| PB0~3            | I/O   | Bit 0~3 for Port B.                                            |  |  |

| PC0~3            | I/O   | Bit 0~3 for Port C.                                            |  |  |

| PD0~1            | I/O   | Bit 0~1 for Port D.                                            |  |  |

| PD2              | I/O   | Bit 2 for Port D                                               |  |  |

| PD3              | I/O   | Bit 3 for Port D. (PD3 for VLN185-5S28J/B, VLN345-5S28J/B)     |  |  |

| PE0~2            | I/O   | Bit 0~2 for Port E. (PE0~3 for VLN185-5S28J/B, VLN345-5S28J/B) |  |  |

| PE3              | I/O   | Bit 3 for Port E                                               |  |  |

| PWM1/DAC         | 0     | PWM1 output or DAC output. ( J type don't support DAC mode)    |  |  |

| PWM2             | 0     | PWM2 output,                                                   |  |  |

#### 5. MEMORY ORGANIZATION

There are maximum 1248K words EPROM, 224 nibbles of RAM and 19 nibbles of dedicated system control register. The registers are divided into 11 nibbles of system registers and 8 nibbles of memory registers. Besides, there are several registers without address allocation, and they can only be accessed by the special instructions. One of the registers is RAM page register (PG), and the others are audio control registers.

#### **5.1 ROM**

A large program/data/voice single ROM is provided, and its structure is shown below. The reserved region contains system information and can't be utilized by users. The program page is limited by the unconditional branch instruction: JMP and CALL. Because it can only handle 14-bit length address of ROM, the program page size is 16K words.

| Address              | ROM                                    |

|----------------------|----------------------------------------|

| 0x000000             | Reset Vector                           |

| 0x00000F             |                                        |

| 0x000010             | Interrupt Vector                       |

| 0x00001E             |                                        |

| 0x00001F             | Reserved                               |

| 0x000BFF             |                                        |

| 0x000C00             | Program & Data Space<br>Program Page 0 |

| 0x003FFF<br>0x004000 | Program & Data Space                   |

#### **5.2 RAM**

Each page of RAM contains 56 nibbles, and VLN5P serial provides 224 nibbles of 4 pages. The page number (PG) register of RAM defined by the MPG instruction, and its initial value is 0. Because the memory space is shared with the memory registers (address=0x00~0x07), the address for RAM is 0x08~0x3F.

In addition to the immediate addressing mode, the indexed addressing mode is also supported. The page and address of the indexed RAM should be stored into RPT1 and RPT0 first, and users can read from or write in the XMD memory register to realize the indexed ROM access.

5

### 6. Clock Generator

The clock generator is a Ring oscillator, and users can select the internal resistor (INT-R). A precise INT-R oscillator is provided, and its accuracy is up to  $\pm 0.5\%$ .

### 7. IO PORTS

There are most 20 I/O ports, designated as PAx through PEx, and x=0~3. All the I/O ports can be configured as input, output, or IO port (bi-direction). For the input port, we provide an internal pull-high register option for convenience. For the output port, users can also option its initial value as low or high according to your application circuit. Besides, users can also enable the large current option for each output port to get a larger sink current. The bi-direction IO port can be an input or output by its register value, and users can option the bi-direction IO with a pull-high resister or without a pull-high resister (Open-Drain). When the register equals 0, it is an output and can only output zero. When the register equals 1, it is a weak pull-high or floating (Open-Drain) so that it also can be considered as an input port with/without a pull-high resistor. Users also can enable the large sink current option of an IO port.

The PX0 port means the PA0, PB0, PC0, PD0, PE0 port can also be optioned as an external reset pin or an infrared (IR) output pin. A reset port can possess a pull-high resister or not, and an IR port can be initial low or high and also large sink current or not.

The pull-high resister of all the I/O ports has two kinds of option: weak and strong. The weak one is about  $850 \text{K}\Omega$  @3V for normal application and the strong one is about  $480 \text{K}\Omega$  @3V usually for key matrix function. When users configure the weak or strong pull-high resister, the pull-high resisters of all I/O ports are set as the option value.

### 8. AUDIO SYNTHESIZER

There are 1-ch voice and 2-ch tone or 4-ch speech/Midi, and all modes are auto-played back by hardware. Different channel mode possesses different hardware structure. It provides a hardware mixer to mix the channel data. The mixer contains a mixer control register MIX. 1-ch ~ 4-ch voice and/or Midi are all configurable by programming the MIX Two audio output stages: DAC and PWM are supported.

#### 8.1 Voice

A voice channel includes a PFLG, a VPR, a voice decoder, a QIO control code generator and an 8-bit sample rate timer (TM) whose timer clock source (TCS) is fixed to 1MHz. It supports PCM and encoded ADPCM speech data.

### 8.2 Tone or Midi

A tone channel includes a TM and an 8-bit envelope (ENV). A Midi channel includes a PFLG, a VPR, a TM, an ENV, a timbre skipper and a multiplier, which multiplies the Midi data and the envelope value held by the

ENV. The timbre skipper is used to fulfill the higher octave pitch playing. The hardware multiplier is dedicated to the Midi channel, and users can't operate it by any instruction.

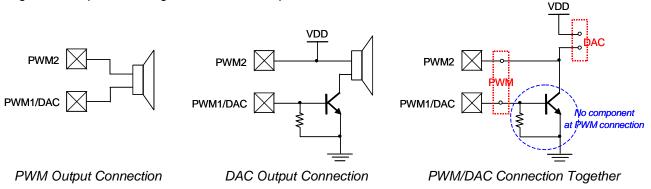

### 8.3 Audio Output

By setting the AUD register, PWM or DAC can be easily chosen as the audio output stage. Besides, it provides a pad detecting mechanism. The pad detecting mechanism detects the PWM2 pad during the reset initialization period, and sets the initial value of the audio output register as PWM if the PWM2 connection is floating, or sets the initial value of the audio output register as DAC if the PWM2 connection is high. In conclusion, connect the speaker to PWM1 and PWM2 only if using PWM, otherwise connect PWM2 to VDD if using DAC. Since the mechanism sets only the initial value of AUD, don't change the value of the AUD register if the pad detecting mechanism is adopted.

When using the PWM output, we provide an option of normal PWM current or large PWM current for different customer demand. The large PWM consumes more current and makes sound louder.

7

#### 8.4 Volume Control

Both PWM and DAC support 16 steps hardware volume control by the VOL register.

# 9. ELECTRICAL CHARACTERISTICS

# 9.1 Absolute Maximum Rating

| Symbol    | Parameter             | Rated Value        | Unit |

|-----------|-----------------------|--------------------|------|

| Vdd - Vss | Supply voltage        | -0.5 ~ +6.0        | V    |

| Vin       | Input voltage         | Vss-0.3V ~ Vdd+0.3 | V    |

| Тор       | Operating Temperature | 0 ~ +70            | °C   |

| Tst       | Storage Temperature   | -25 ~ +85          | °C   |

# 9.2 DC Characteristics

| Symbol           | Parameter                          |                  | VDD | Min.          | Тур.  | Max.          | Unit   | Condition                           |

|------------------|------------------------------------|------------------|-----|---------------|-------|---------------|--------|-------------------------------------|

| VDD              | Operating voltage                  |                  |     | 2.0           | 3     | 5.5           | V      | 1 MHz                               |

| İsb              |                                    | Halt             | 3   |               |       | 1             | uA     | Class as leading                    |

| ISD              |                                    | mode             | 4.5 |               |       | 1             |        | Sleep, no loading                   |

| İsi              | Supply                             | Slow             | 3   |               | 75    |               | uA     | 1ms interrupt, no load              |

| 131              | current                            | mode             | 4.5 |               | 100   |               | u/\    | This interrupt, no load             |

| lop              |                                    | Operating        | 3   |               | 4/4.5 |               | mA     | 1/2 MHz, no loading                 |

| юр               |                                    | mode             | 4.5 |               | 5/5.5 |               | 1117 ( | 172 1711 12, 110 10441119           |

|                  |                                    | Weak             | 3   |               | -3.5  |               |        |                                     |

| lii              | Input current<br>(Internal         | (850k ohms)      | 4.5 |               | -10   |               | uA     | Vil=0v                              |

| ""               | pull-high)                         | Strong           | 3   |               | -7    |               | u A    | VII—UV                              |

|                  |                                    | (480k ohms)      | 4.5 |               | -20   |               |        |                                     |

| loh              | Output h                           | igh current      | 3   |               | -7    |               | mΛ     | Voh=1.0V                            |

| ION              | Output III                         | ign current      | 4.5 |               | -11   |               | mA     | Voh=2.2V                            |

| lol              | Output lo                          |                  | 3   |               | 10    |               | mA     | Vol=2.0V                            |

| 101              | (Norma                             | l current)       | 4.5 |               | 15    |               | MA     | Vol=2.5V                            |

| lol              | Output low current (Large current) |                  | 3   |               | 20    |               | m A    | Vol=2.0V                            |

| 101              |                                    |                  | 4.5 |               | 25    |               | mA     | Vol=2.5V                            |

| I <sub>PWM</sub> |                                    | put current      | 3   |               | 60    |               | mA     | Load=8 ohms                         |

| IPWM             | (No                                | rmal)            | 4.5 |               | 100   |               | ША     | Loau=o onins                        |

| Iрwм             | PWM out                            | put current      | 3   |               | 70    |               | mA     | Load=8 ohms                         |

| IPWM             | (La                                | arge)            | 4.5 |               | 117   |               | ША     | Loau=o onins                        |

| A F/F            | Frequency deviation                |                  | 3   |               | 1.5   |               | 0/     | Fosc(3.0v)-Fosc(2.4v)<br>Fosc(3v)   |

|                  |                                    | age drop<br>ИНz) | 4.5 |               | 0.5   |               | %      | Fosc(4.5v)-Fosc(3.0v)<br>Fosc(4.5v) |

| Δ F/F            | Frequency lot deviation (1MHz)     |                  | 3   | -1            |       | 1             | %      | Fmax(3.0v)-Fmin(3.0v)<br>Fmax(3.0v) |

| Fosc             | Oscillation Frequency              |                  | -   | 0.97<br>/1.94 | 1/2   | 1.03<br>/2.06 | MHz    | VDD=2.0~5.5V                        |

8

# 10. APPLICATION

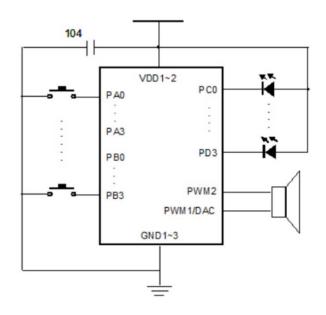

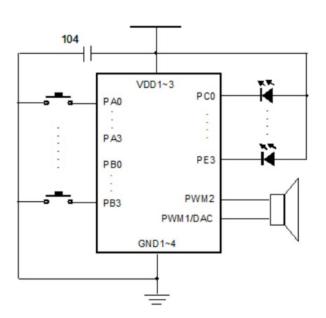

# 10.1 VLN025-5S24J/B, VLN085-5S24J/B

# (1) PWM Direct-Drive

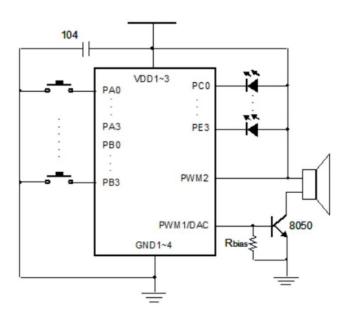

### (2) DAC Direct-Drive

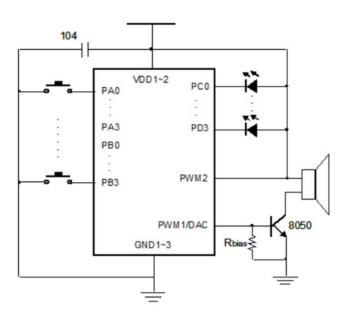

# 10.2 VLN185-5S28J/B, VLN345-5S28J/B

### (1) PWM Direct-Drive

# (2) DAC Direct-Drive

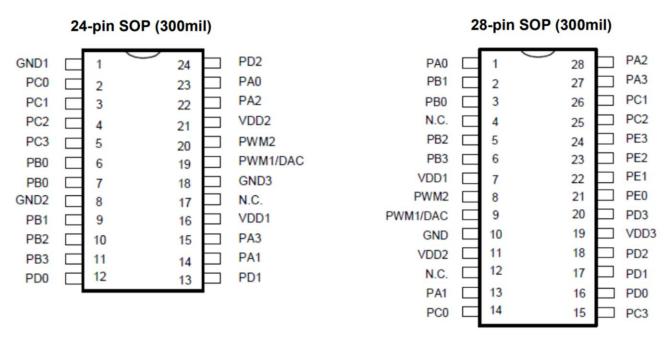

# 11. PACKAGE PIN ASSIGNMENT

10

VLN025/085-5S24J/B

(J type don't support DAC mode)

Ver. 2.0 2018/6/18

VLN185/345-5S28J/B

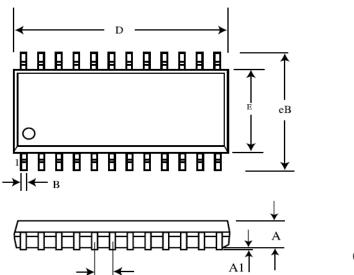

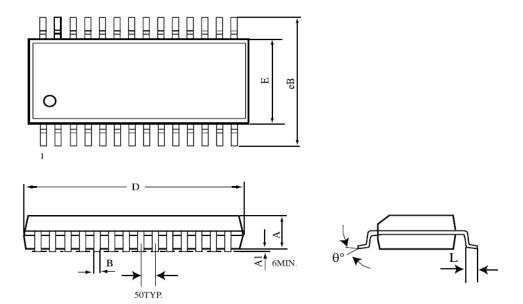

# 12. PACKAGE DIMENSION

# 24-Pin Plastic SOP (300 mil)

| Sym.             | Dimension in mils |      |      | Dimension in mm |        |        |

|------------------|-------------------|------|------|-----------------|--------|--------|

|                  | Min.              | Nom. | Max. | Min.            | Nom.   | Max.   |

| A                | 98                | 100  | 102  | 2.489           | 2.540  | 2.591  |

| A1               | 6                 |      |      | 0.152           |        |        |

| В                | 12                | 16   | 20   | 0.305           | 0.406  | 0.508  |

| D                | 606               | 608  | 610  | 15.392          | 15.443 | 15.494 |

| Е                | 298               | 300  | 302  | 7.569           | 7.620  | 7.671  |

| eB               | 406               | 410  | 414  | 10.312          | 10.414 | 10.516 |

| L                | 25                |      |      | 0.635           |        |        |

| $\theta^{\circ}$ | 0°                | 4°   | 8°   | 0°              | 4°     | 8°     |

11

# 28-Pin Plastic SOP (300 mil)

| Sym.       | Dimen       | Dimension in mils |      |        | Dimension in mm |        |  |

|------------|-------------|-------------------|------|--------|-----------------|--------|--|

|            | Min.        | Nom.              | Max. | Min.   | Nom.            | Max.   |  |

| A          | 90          | 92                | 94   | 2.286  | 2.337           | 2.388  |  |

| Al         | 6           |                   |      | 0.152  |                 |        |  |

| В          | 12          | 16                | 20   | 0.305  | 0.406           | 0.508  |  |

| D          | 703         | 705               | 707  | 17.856 | 17.907          | 17.958 |  |

| Е          | 293         | 295               | 297  | 7.442  | 7.493           | 7.544  |  |

| eB         | 406         | 410               | 414  | 10.312 | 10.414          | 10.516 |  |

| L          | 25          |                   |      | 0.635  |                 |        |  |

| $\theta$ ° | $0^{\circ}$ | 4°                | 8°   | 0°     | 4°              | 8°     |  |

# 13. ORDERING INFORMATION

| P/N         | Shipping Type | Remarks       |

|-------------|---------------|---------------|

| VLN025-5S24 | SOP-24        | Width 300 mil |

| VLN085-5S24 | SOP-24        | Width 300 mil |

| VLN185-5S28 | SOP-28        | Width 300 mil |

| VLN345-5S28 | SOP-28        | Width 300 mil |

13